Задание в формате PDF ~185KБ тыц

Интерфейс модуля:

Входной потоковый интерфейс

| snk_reset | вход | Асинхронный сброс для входного потокового интерфейса |

| snk_clock | вход | Тактовый сигнал для входного потокового интерфейса |

| snk_ready | выход | Сигнал готовности входного потокового интерфейса. Если 0, то модуль не готов принимать новую транзакцию (занят сортировкой или отправкой выходной транзакции и пр.) |

| snk_valid | вход | Подтверждает валидность snk_sop, snk_eop, snk_data |

| snk_sop | вход | Начало транзакции (первое слово) |

| snk_eop | вход | Конец транзакции (последнее слово) |

| snk_data | вход | Слово данных |

Выходной потоковый интерфейс

| src_reset | вход | Асинхронный сброс для выходного потокового интерфейса |

| src_clock | вход | Тактовый сигнал для выходного потокового интерфейса |

| src_valid | выход | Подтверждает валидность src_sop, src_eop, src_data |

| src_sop | выход | Начало транзакции (первое слово) |

| src_eop | выход | Конец транзакции (последнее слово) |

| src_data | выход | Слово данных |

Параметры модуля:

| DATA_WIDTH | Ширина слов (snk_data, src_data) |

| MAX_LENGTH | Максимальная длина транзакции |

На модуль подаются данные в неотсортированном виде через входной потоковый интерфейс на частоте 50МГц.

Необходимо сформировать поток отсортированных по возрастанию данных через выходной потоковый интерфейс на частоте 133МГц.

Чтобы запретить приём новых транзакций во время обработки входных данных, можно опускать сигнал snk_ready в 0.

Транзакции на вход и на выход должны быть непрерывны: опускания в 0 сигналов snk_valid и src_valid во время транзакции недопустимы.

Гарантируется, что:

Алгоритм сортировки можно выбрать любой, однако, постарайтесь выбрать тот, который будет давать минимальную задержку.

На время работы модуля будет влиять не только выбранный алгоритм, но и собственно его реализация (“правильное” использование двухпортовой памяти и прочие трюки).

Перевёл на русский язык видео Intel по High-Level Synthesis. Всего 3 части. Просто как возможная идея реализации сортировки или Test Bench.

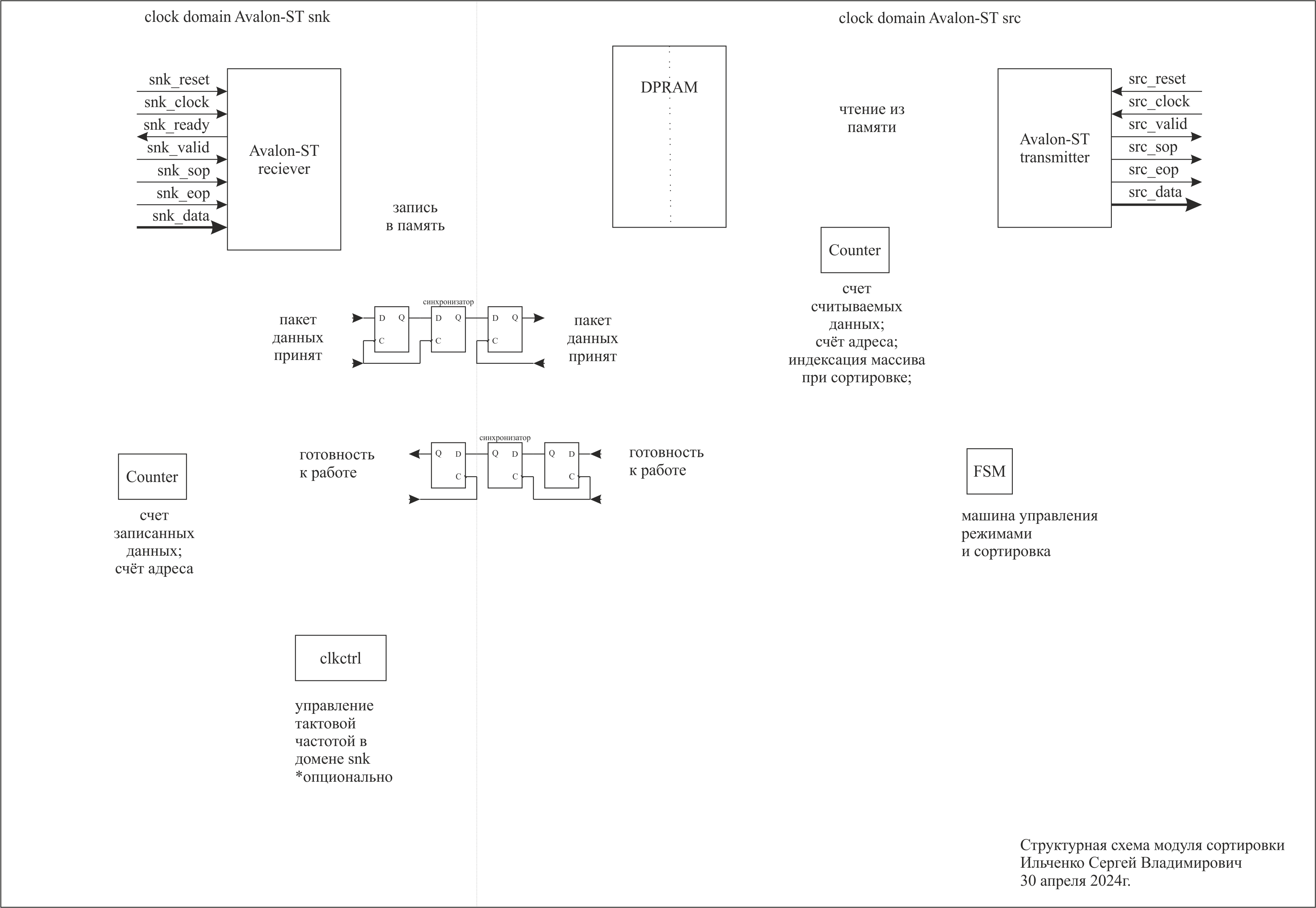

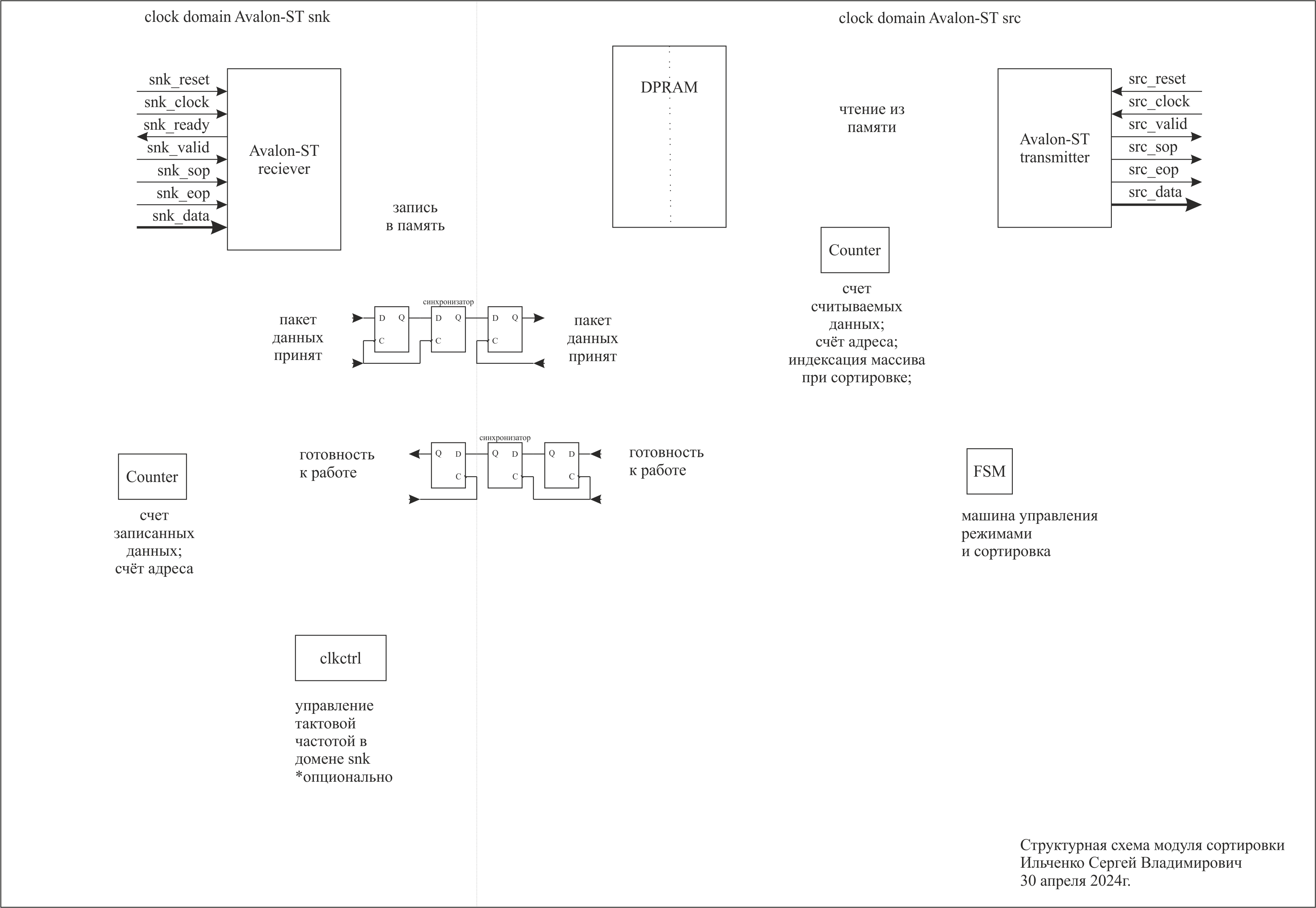

Разработал структурную схему модуля сортировки (будет обновляться в процессе разработки).

PDF ~1,33МБ: тыц

PNG (изображение откроется в новой вкладке) ~421KБ: тыц

Verilog код двухпортовой RAM представлен ниже.

Запросим у ChatGPT 3.5 описание входного интерфейса на Verilog и попросим сгенерировать файл временных ограничений. Описав следующим текстом желаемый алгоритм поведения:

Здравствуй. Напиши пожалуйста Verilog код делающий следующее: шина Avalon-ST синхронная пакетная передача. Схема сбрасывается асинхронным сбросом, активный высокий уровень: "snk_reset". Тактовый сигнал называется "snk_clock" частота 50МГц. Если сигнал валидности snk_valid установлен в единицу то:

переход сигнала snk_sop из ноля в единицу сбрасывает 10 разрядный счетчик адреса;

сигнал записи в память WE также устанавливается равным единице.

Напиши пожалуйста файл констрейнов SDC для такой схемы.

Видео процесса запроса представлено ниже.

Сгенерированный ChatGPT 3.5 Verilog код Avalon-ST snk приведён ниже.

Сгенерированный ChatGPT 3.5 текст временных ограничений приведён ниже.

Аналогичным образом запросим код потоковой передачи Avalon-ST и текст временных ограничений.

Здравствуй. Напиши пожалуйста Verilog код делающий следующее: Шина Avalon-ST синхронная пакетная передача. Схема сбрасывается асинхронным сбросом, активный высокий уровень: "src_reset". Тактовый сигнал называется "src_clock", частота 133МГц. Выполняется считывание из синхронной памяти разрядностью 32 бит и глубиной 1024 слов. Память адресуется счётчиком адреса "src_addr_counter". По внешнему сигналу "w_export" запускается считывание из памяти и передача на шину Avalon-ST, причём начало пакетной передачи утверждается сигналом "src_sop" равным логической единице, длительность 1 такт. Окончание пакетной передачи утверждается сигналом "src_eop" равным логической единице, длительность 1 такт. Всё время передачи, данные сопровождаются сигналом "src_valid" равным логической единице, всё остальное время сигнал установлен равным логическому ноль

И второй запрос:

Напиши пожалуйста файл констрейнов SDC для такой схемы.

Видео процесса запроса представлено ниже.

Сгенерированный ChatGPT 3.5 Verilog код Avalon-ST src приведён ниже.

Сгенерированный ChatGPT 3.5 текст временных ограничений приведён ниже.

Намеренно отказываясь на данном этапе разработки от выбора оптимального алгоритма сортировки, воспользуемся описанием сортировки пузырьком с сайта СПбГУ ИТМО. Не будем оценивать сложность алгоритмов и скорость работы.

Адаптированный текст программы на языке Си приведён ниже.

Видео процесса сборки, отладки проекта в среде Microsoft Visual Studio и демонстрация работоспособности представлено ниже.

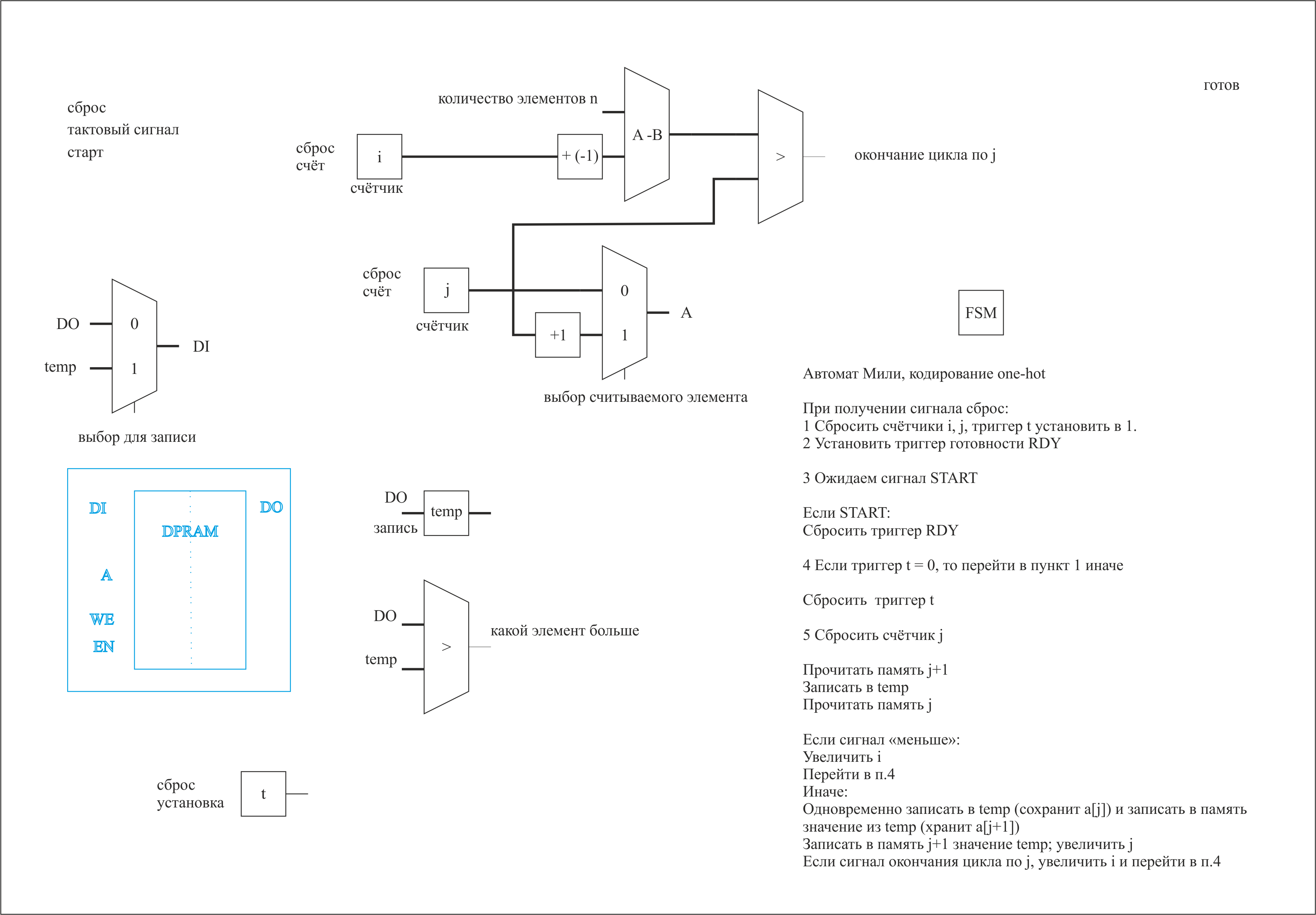

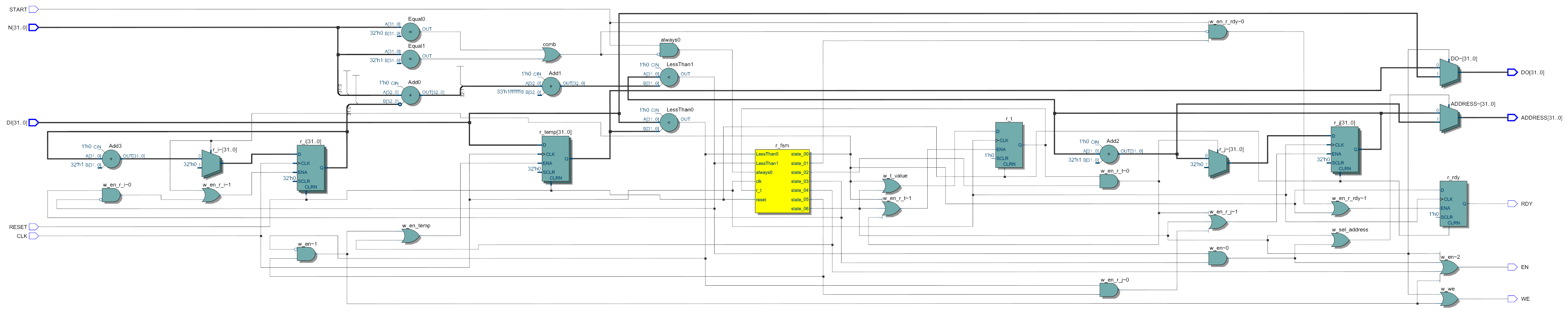

Разработал структурную схему модуля сортировки на основании подпрограммы сортировки на языке Си (будет обновляться в процессе разработки). Определил основные операционные узлы такие как счётчики i, j; регистры: "готовности" и "цикла"; мультеплексоры шин, сумматоры, компараторы. Подразумевается, что блок синхронной памяти будет находится вне модуля (помечен синим цветом). Описал текстом алгоритм стейт-машины.

PDF ~1,33МБ: тыц

PNG (изображение откроется в новой вкладке) ~469KБ: тыц

Купил отладочную плату.

Пишу и одновременно отлаживаю модуль сортировки пузырьком.

Verilog код модуля bublesort.v представлен ниже.

Verilog код модуля test_bench.v представлен ниже.

Схема модуля.

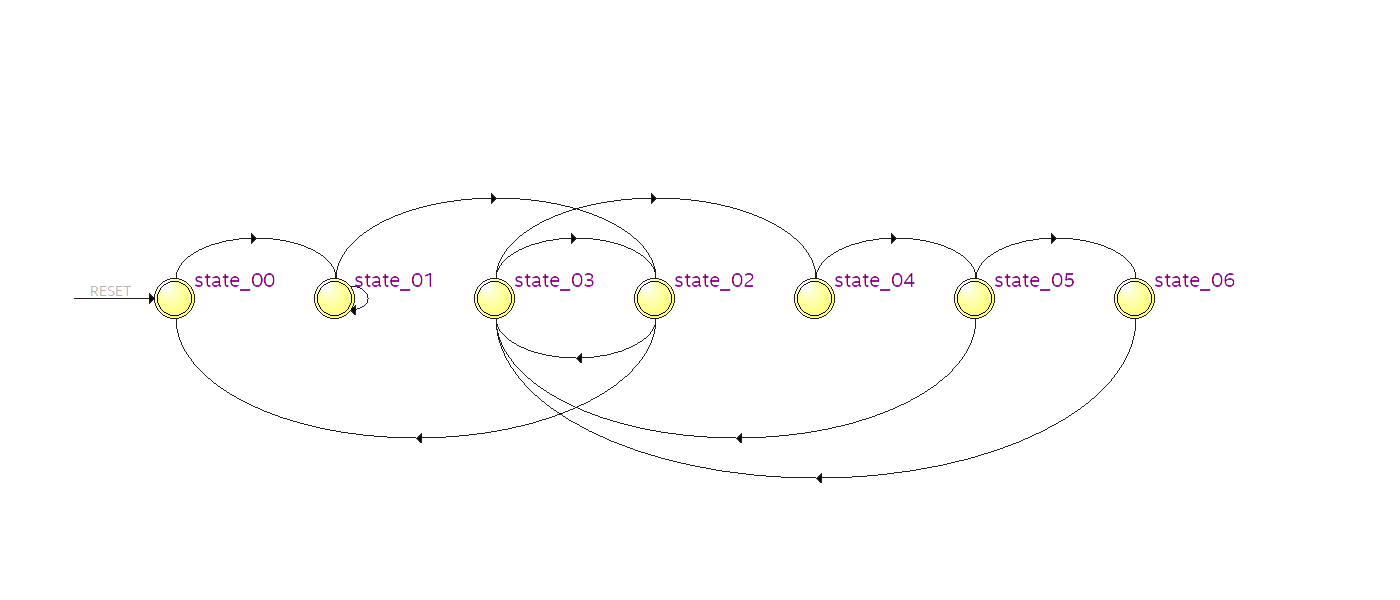

Диаграмма машины состояний.